Dr.KALAMANI C

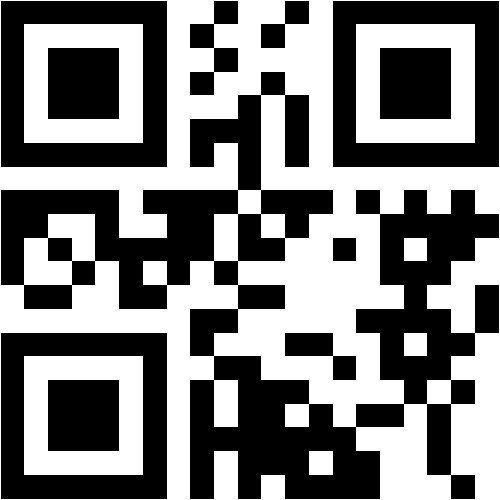

@tnce.in

Professor and ECE

Tamilnadu College of Engineering

EDUCATION

B.E,M.Tech,P.hD

RESEARCH, TEACHING, or OTHER INTERESTS

Electrical and Electronic Engineering, Control and Systems Engineering, Industrial and Manufacturing Engineering, Architecture

Scopus Publications

Scholar Citations

Scholar h-index

Scholar i10-index

Scopus Publications

C. Kalamani, R. Murugasami, S. Usha, and S. Saravanakumar

Elsevier BV

C. Kalamani, S. Lekashri, A.N. Duraivel, and T. Selvin Retna Raj

Informa UK Limited

ABSTRACT The digital filters play a significant role in the field of digital signal processing (DSP). The finite impulse response (FIR) filter is an attractive choice because of the ease of design and good stability. The digital filters have a wide variety of applications such as signal processing, control systems, telecommunication, etc. They are better than the analogue filters due to their performance. In recent times, software radios have achieved attention owing to requirements for integrated and reconfigurable communication systems. Hence, reconfigurations have emerged as a significant problem in the designs of FIRs. To match the frequencies of DSP applications, higher-order FIRs are required. If length of filters rises, addition and multiplication operations also increase. This paper proposes an efficient hardware design of RFIR that employs modified bacterial foraging optimizations (MBFOs) and common sub-expression eliminations (CSEs) in its executions. MBFOs output restricted counts of filter coefficients with sums of signed-power-of-two (SPT) terms while maintaining the quality of filtered responses. On obtaining coefficients, eliminations are executed by CSEs where hardware complexities are determined in terms of adders. Model sim software validated RFIRs using the Verilog code. The proposed design of RFIRs was compared with existing designs in terms of power usages, frequencies and areas.

Rajadurai S, Dhinesh N, Karthikeyan S, and Kalamani C

IEEE

Attendance tracking is critical to monitoring student or employee attendance in academic and organizational settings. With the rise of online education and remote work, traditional attendance tracking methods are becoming less effective. This paper proposes a web application for an image- based online attendance tracking system (PATSO) that utilizes machine learning algorithm SVM for classification and face recognition technique to identify and track attendance. The system gets a group or an individual image of students from the user and compares them to a pre-stored database of images to verify attendance. The proposed method is convenient, and accurate, and eliminates the need for manual attendance tracking not only in online mode but also in offline modes. The system's effectiveness was evaluated through a series of experiments, which showed a high accuracy rate of over 90%.

Kalamani C., Kamatchi S., Sasikala S., and Murali L.

Informa UK Limited

Kalamani. C, Dharani, Vanjipriya, and Ishwarya Niranjana. M

IEEE

In applications involving image processing, multipliers are crucial. Area, potency, and delay analysis of the circuit are a few of the different metrics used to describe the performance of digital analysis. The 4-bit AXB is multiplied by a 4X4 Wallace tree resulting in the formation of a fractional creation, which causes an incrimination in latency. The delay is further decremented by inserting a 4-2 compressor in the fractional creation generation phase and it is used to implement 8bit Wallace multiplier to reduce delay. The simulated result shows a decrease in power and delay.

Kalamani. C, Abiramasundari. S, Dhanasekar. J, and Ishwarya Niranjana. M

IEEE

Microstrip patch antennas are castoff in various applications. It uses resonant cavity for its radiation. The various antennas are designed in the past. The proposed antennas are designed with single patch, array with rectangular structure and array antenna with circular structure using ADS software. Both single and array with rectangular are operating in three band of frequency at 4.5,5. 7and 7.6 Giga hertz. The performances of these antennas are increased by inserting λ/4 between transmission line and patch. The performances improve further by making circular structure. This circular structure is operating in the 5.8 Gigahertz and used in RFID and WLAN application.

Kalamani C, Vivek Karthick Perumal, M. Vivek Kumar, and J. Muralidharan

IEEE

A power, delay efficient error acquiescent adder is proposed. In recent VLSI expertise, the manifestation of all categories of faults has developed foreseeable. By embracing an emergent perception in VLSI strategy, fault-tolerant adder (FTA) is suggested. The FTA is talented to comfort the harsh constraint on exactitude, and at the identical period accomplish marvelous enhancements in together the power ingestion and speediness enactment. For any transportable uses anywhere the power ingestion and speed are the utmost significant limit, one must diminish the power feeding and upsurge the speed as ample as probable. In this technique certain amendments are suggested to predictable adders to significantly decrease its power feeding. The amendments to the conservative building comprise the elimination of carry generation from LSB to MSB. With this the adder works at high speed with low power consumption.

Vivek Kumar M, Ram Sundar. G, Manoharan. K, Kalamani. C, and Soumiya. S

IEEE

The most important prerequisite for providing advanced patient care in hospitals is hydration and electrolyte assessment and management. Electrolyte levels are manually checked in almost all hospitals. The patient's mortality could result from an incorrect bottle replacement. When the nurse failed to notice the notification or forget to replace the bottle once it gets emptied, there will be a high risk of reverse flow of blood. When the air gets locked up or the bottle gets emptier, it may lead to death of the patient. The proposed system monitors the entire process automatically. The setup also intimates the user through alert messages and notification at times. A warning popup notification is sent to the in charge/nurse and the caregivers based on the electrolyte levels with a unique key (room id & patient id). If they failed to notice the message and replace it, the smart tuning mechanism will block the fluid path and eliminates the reverse blood flow and the whole process stops automatically. Hence, there will not be any reverse blood flow or air bubble forming, which leads to death.

Kalamani C, Pradeesh Kumar S, Kowsalya V, and Vinith Rahul M

IEEE

In this paper, Head Gestures has been defined as the mode of conversation while interacting with the robot. The head gesture robotic is really helpful to limit human efforts and lift out fantastic results. Head gesture robot makes use of the easy module like Arduino, gyroscope and RF Module, which is discovered to be positive than different Wi-Fi module. The gyroscope relies upon the gestures of the head. Through gyroscope, a passage of data signal is obtained and it is processed with assist of aruino microcontroller. In three-axis gyroscope, one axis will govern the pace in ahead or backward course and different axis will alter the spinning mechanism. The microcontroller provided instructions to the robot to travel in the prefered direction. The primary working precept for the robotic is passage of the records indicators of gyroscope readings to the arduino board equipped on the bot. The usage of the eye blink sensor in the transmitter helps to automatic turn on/off the robot. The software compiled in that arduino runs in accordance to that value, which make the bot characteristics accordingly.

C. Kalamani, M. Mayilsamy, V. Rukkumani, K. Srinivasan, R. Mohan Kumar, and K. Paramasivam

Elsevier BV

C. Kalamani

Elsevier BV